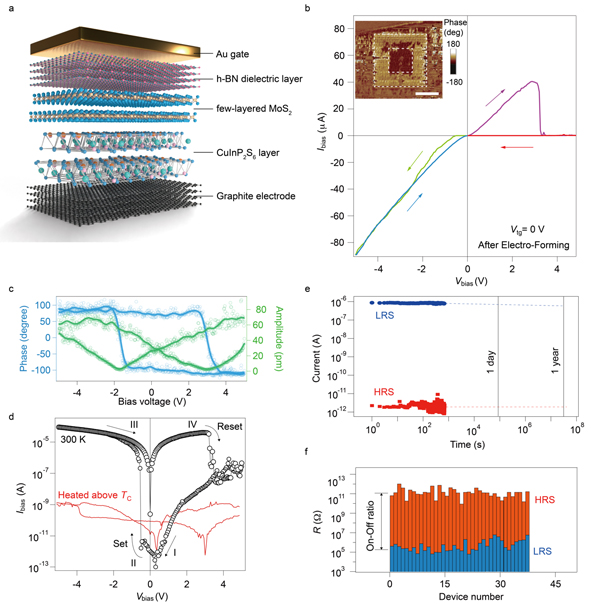

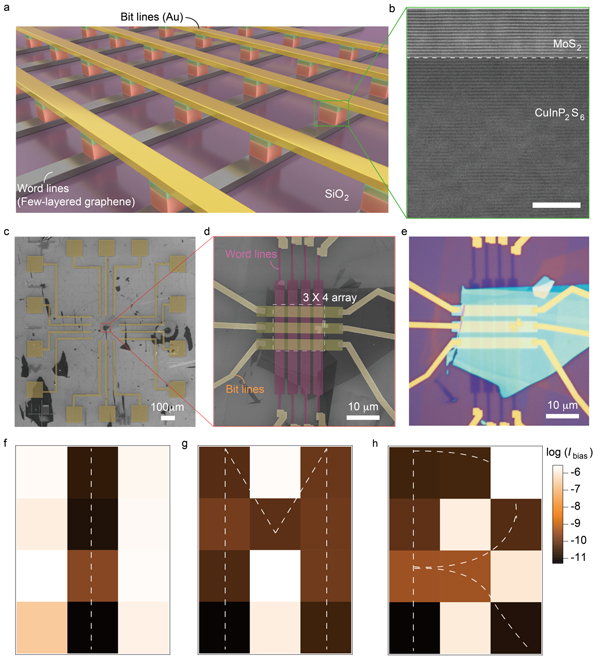

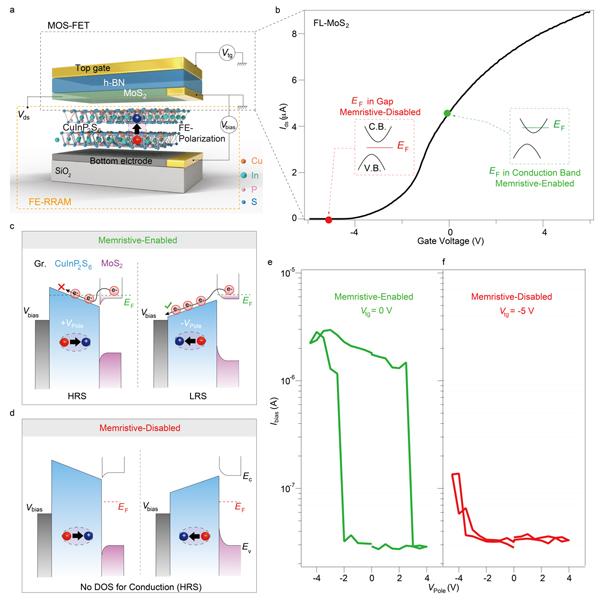

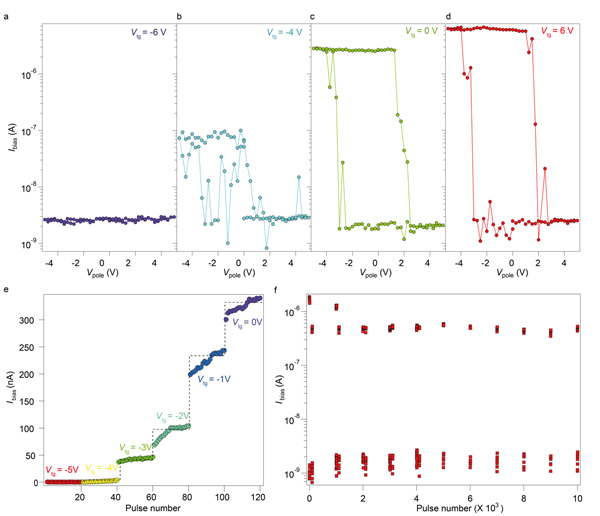

研究团队使用二维层状材料CuInP2S6作为铁电绝缘体层,利用二维层状半导体材料MoS2和多层石墨烯分别作为铁电忆阻器的上、下电极层,形成金属/铁电体/半导体(M-FE-S)架构的忆阻器;同时,在顶部半导体层上方通过堆叠多层h-BN作为栅极介电层引入了MOSFET架构。底部M-FE-S忆阻器件开关比超过105并且具有长期数据存储能力,且阻变行为与CuInP2S6层的铁电性存在较强耦合(图1)。此外,研究人员通过制备3 4的阵列结构,展示了该型铁电忆阻器件应用于存储交叉阵列(crossbar array,实现随机存取存储器(RAM)的关键结构)的可行性(图2)。进一步,研究人员通过在上方MOSFET施加栅极电压,有效调控了二维半导体层MoS2的载流子浓度(或费米能级),从而对下方M-FE-S忆阻器的存储性能进行操控(图3)。基于以上结果,研究人员展示了该型器件的门电压可调多阻态的存储特性(图4)。

本研究所展示的门电压可编程的铁电忆阻器有望在未来人工突触等神经形态计算系统中发挥重要作用,并可能引发基于二维铁电材料制备多功能器件的开发。此外,该工作所提出的MOSFET与忆阻器垂直集成的架构可以进一步扩展到其他二维材料体系,从而获得性能更加优异的新型存储器。

该项研究由中科院金属所王汉文助理研究员主导,国内外多家单位合作完成,博士生李婉莹和郭艺萌为共同第一作者。工作得到了国家重点研发计划青年项目、国家自然科学基金青年项目/面上项目/联合培育项目、沈阳材料科学国家研究中心等项目支持。

图1 器件结构设计及两端铁电忆阻器的存储性能。a)器件结构示意图。b)器件的阻变行为。c)少层CuInP2S6的压电力显微镜相位和幅值图。d)器件在不同温度下的输运行为。e)存储器的数据保持能力测试。f)存储器开关比统计图。

图2 铁电忆阻器存储阵列演示。a)二维铁电RAM结构示意图。b)CuInP2S6/MoS2界面的HAADF-STEM照片。c)3 4阵列的SEM图像。d)局部放大图。e)3 4阵列的光学照片。f-g)通过读取3 4阵列中每个交叉点的高阻态和低阻态编码的“I”、“M”和“R”的简化字母。

图3 器件的可编程存储特性。a)器件结构示意图。b)MoS2层的转移特性曲线。c-d)异质结的能带结构图。e-f)通过施加门电压实现了对存储窗口从有到无的调控。

图4 门电压可编程存储器的多阻态存储特性。a-d)器件在不同门电压下的存储窗口。e)器件的多阻态存储性能演示。f)栅极调控的耐疲劳特性。